1.

Rangkaian Logika Sekuensial

Pada rangkaian logika sekuensial, keadaan keluaran selainditentukan oleh keadaan masukan juga ditentukan olehkeadaan keluaran sebelumnya. Hal itu menunjukkan bahwarangkaian logika sekuensial harus mempunyai pengingat(memory), atau kemampuan untuk menyimpan informasi.Rangkaian dasar yang dapat dipakai untuk membentukrangkaian logika sekuensial adalah latch dan flip-flop.Perbedaan latch dan flip-flop terletak pada masukanclock. Pada flip-flop dilengkapi dengan masukan clock,sedangkan pada latch tidak. Flip-flop hanya akan bekerjapada saat transisi pulsa clock dari tinggi ke rendah ataudari rendah ke tinggi, tergantung dari jenis clock yangdigunakan. Transisi pulsa clock dari rendah ke tinggi disebut transisi positif, sedangkan transisi tinggi kerendah di sebut transisi negatif.

1. RS FLIP-FLOP

Flip-flop RS atau SR (Set-Reset) merupakan dasar dari flip-flop jenis lain. Flip-flop ini mempunyai 2 masukan: satu disebut S (SET) yang dipakai untuk menyetel (membuat keluaran flip-flop berkeadaan 1) dan yang lain disebut R (RESET) yang dipakai untuk me-reset (membuat keluaran berkeadaan 0).

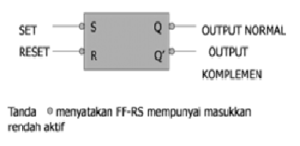

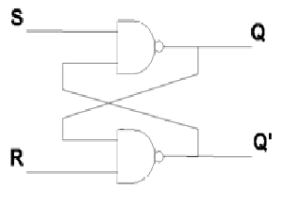

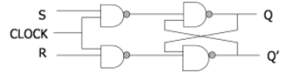

a. FF-RS (dirangkai dari NAND gate)

Rangkaian Logika FF-RS

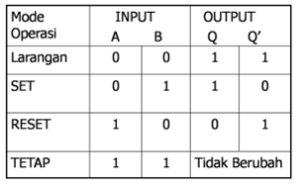

Tabel Kebenaran FF RS

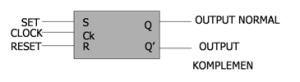

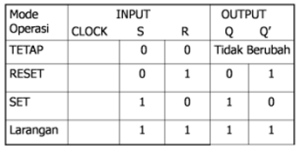

b. FF – RS Berdetak

Dengan adanya detak akan membuat FF-RS bekerja sinkron atau aktif HIGH

Simbol Logika

Rangkaian Logika FF-RS Berdetak

Tabel Kebenaran FF-RS Berdetak

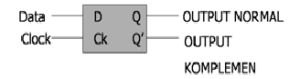

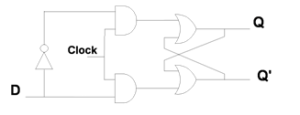

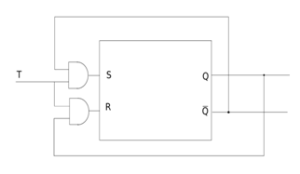

2. D FLIP-FLOP

Sebuah masalah yang terjadi pada Flip-flop RS adalah dimana keadaan R = 1, S = 1 harus dihindarkan. Satu cara untuk mengatasinya adalah dengan mengizinkan hanya sebuah input saja dimana FF-D mampu mengatasi masalah tersebut

Simbol Logika

Rangkaian Logika

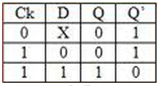

Tabel Kebenaran

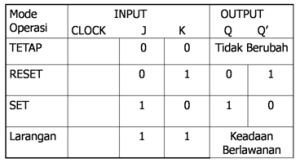

3. JK FLIP-FLOP

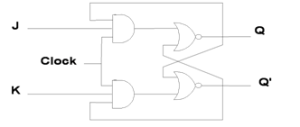

FF JK mempunyai masukan “J” dan “K”. FF ini “dipicu” oleh suatu pinggiran pulsa clock positif atau negatif. FF JK merupakan rangkaian dasar untuk menyusun sebuah pencacah. FF JK dibangun dari rangkaian dasar FF SR dengan menambahkan dua gerbang AND pada masukan R dan S serta dilengkapi dengan rangkaian diferensiator pembentuk denyut pulsa clock

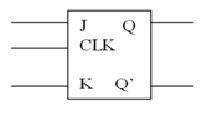

Simbol logika

Rangkaian Logika

Tabel Kebenaran

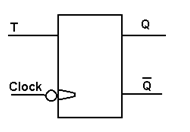

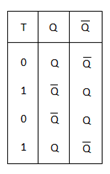

4. T FLIP-FLOP

Nama flip-flop T diambil dari sifatnya yang selalu berubah keadaan setiap ada sinyal pemicu (trigger) pada masukannya. Input T merupakan satu-satunya masukan yang ada pada flip-flop jenis ini sedangkan keluarannya tetap dua, seperti semua flip-flop pada umumnya. Kalau keadaan keluaran flip-flop 0, maka setelah adanya sinyal pemicu keadaan-berikut menjadi 1 dan bila keadaannya 1, maka setelah adanya pemicuan keadaannya berubah menjadi 0. Karena sifat ini sering juga flip-flop ini disebut sebagai flip-flop toggle (berasal dari scalar toggle/pasak).

Simbol Logika

Rangkaian Logika

Tabel Kebenaran

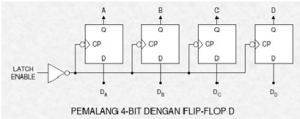

5. REGISTER

Register adalah himpunan dari sejumlah sel yang masing-masing terdiri dari sebuah flip-flop, dimana setiap sel dapat menyimpan data sebanyak 1-bit. Register ini umumnya dapat dibaca dan ditulis sehingga berfungsi sebagai memori yang berukuran kecil. Fungsi dari register kadang-kadang lebih dari hanya sekedar menyimpan data, tetapi dapat juga mengolahnya secara terbatas, misalnya menggeser kekiri atau kekanan.

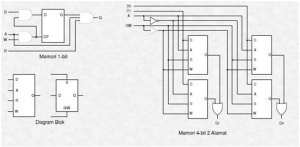

Register Pemalang (Latch)

Disebut pemalang karena register ini berfungsi untuk memalang data. Artinya nilai data yang menjadi masukannya akan dipertahankan pada keluarannya, walaupun masukan tersebut telah dihilangkan. Register ini sangat diperlukan untuk menghubungkan peralatan berkecepatan tinggi dengan yang berkecepatan rendah. Dalam hal ini register berfungsi sebagai penyangga (buffer). Pemalang umumnya dibentuk dengan menggunakan flip-flop D.

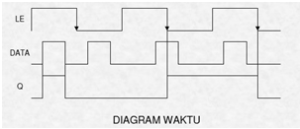

Jika masukan LE (Latch Enable) tinggi maka semua flip-flop mendapat pulsa clock sehingga menangkap data masukannya. Selanjutnya jika data masukan dihilangkan maka nilai data sebelumnya akan tetap ada pada keluaran register. Data ini akan tetap dipertahankan sampai ada pengambilan data yang baru.

Pemalang Transparan

Pemalang umumnya dibuat transparan dimana masukan LE bersifat level sensitive. Jika LE bernilai tinggi maka nilai keluaran flip-flop yang bersangkutan akan sama dengan nilai keluarannya. Saat LE beralih ke rendah maka nilai masukan pada saat itu akan ditangkap dan dipertahankan.

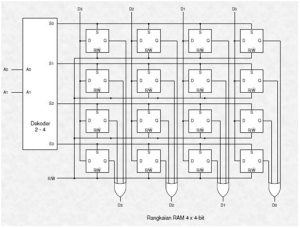

Memori

Memori berfungsi untuk menyimpan informasi. Jumlah data yang dapat disimpan tergantung kapasitas memori tersebut. Ada memori yang hanya dapat dibaca (ROM) ada pula yang dapat dibaca dan ditulis (RAM)

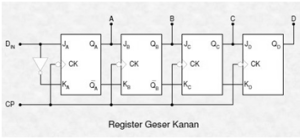

Register Geser Kanan

Pada register ini flip-flop yang dikanan mendapat masukan dari keluaran flip-flop yang dikiri.

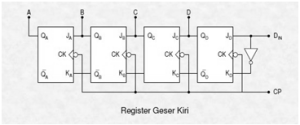

Register Geser Kiri

Pada register ini flip-flop yang dikiri mendapat masukan dari keluaran flip-flop yang dikanan.

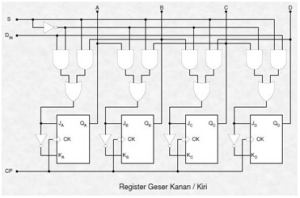

Register Geser Kanan / Kiri

Masukan suatu flip-flop bisa dari flip-flop yang dikiri ataupun yang dikanannya, tergantung pada nilai logika masukan S (select).

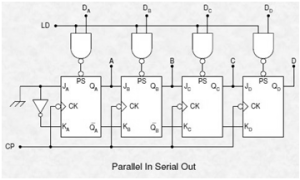

Parallel Input Serial Output

Data untuk masing-masing flip-flop akan di-loading pada saat masukan LD (load) berlogika tinggi. Selanjutnya data akan digeser kekanan pada setiap pulsa CP.

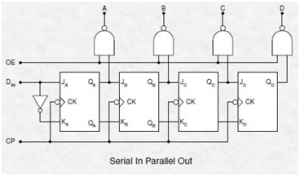

Serial Input Parallel Output

Data untuk masing-masing flip-flop akan dikeluarkan pada saat masukan OE (output enable) berlogika tinggi.

2.

Rangkaian Logika Kombinasional

Rangkaian kombinasional terdiri dari gerbang logika yang memiliki output yang selalu tergantung pada kombinasi input yang ada. Rangkaian kombinasional melakukan operasi yang dapat ditentukan secara logika dengan memakai sebuah fungsi boolean.

Ada beberapa Rangkaian logika kombinasional yang akan dibahas adalah Enkoder, Dekoder, Multiplexer, dan Demultiplexer.

1. Enkoder

Enkoder adalah rangkaian logika kombinasional yang berfungsi untuk mengubah atau mengkodekan suatu sinyal masukan diskrit menjadi keluaran kode biner.

Enkoder disusun dari gerbanggerbang logika yang menghasilkan keluaran biner sebagai hasil tanggapan adanya dua atau lebih variabel masukan. Hasil keluarannya dinyatakan dengan aljabar boole, tergantung dari kombinasi – kombinasi gerbang yang digunakan.

Sebuah Enkoder harus memenuhi syarat perancangan m < 2 n . Variabel m adalah kombinasi masukan dan n adalah jumlah bit keluaran sebuah enkoder. Satu kombinasi masukan hanya dapat mewakili satu kombinasi keluaran.

2. Dekoder

Rangkaian Dekoder mempunyai sifat yang berkebalikan dengan Enkoder yaitu merubah kode biner menjadi sinyal diskrit. Sebuah dekoder harus memenuhi syarat perancangan m < 2 n . Variabel m adalah kombinasi keluaran dan n adalah jumlah bit masukan. Satu kombinasi masukan hanya dapat mewakili satu kombinasi keluaran.

3. Rangkaian logika kombinasional Multiplexer

Rangkaian logika kombinasional Multiplexer atau disingkat MUX adalah alat atau komponen elektronika yang bisa memilih input (masukan) yang akan diteruskan ke bagian output (keluaran). Pemilihan input mana yang dipilih akan ditentukan oleh signal yang ada di bagian kontrol (kendali) Select.

4. Rangkaian Logika kombinasional Demultiplekser

Rangkaian logika kombinasional Demultiplekser adalah Komponen yang berfungsi kebalikan dari MUX. Pada DEMUX, jumlah masukannya hanya satu, tetapi bagian keluarannya banyak. Signal pada bagian input ini akan disalurkan ke bagian output (channel) yang mana tergantung dari kendali pada bagian SELECTnya.

– Suatu rangkaian diklasifikasikan sebagai kombinasional jika memiliki sifat yaitu keluarannya ditentukan hanya oleh masukkan eksternal saja.

– Suatu rangkaian diklasifikasikan sequential jika ia memiliki sifat keluarannya ditentukan oleh tidak hanya masukkan eksternal tetapi juga oleh kondisi sebelumnya.

MODEL RANGKAIAN KOMBINASIONAL

Dengan :

F1 = F1 (I1, I2,…In ; t1 = F1 setelah ?t1

F2 = F2 (I1, I2,…In ; t2 = F2 setelah ?t2

– – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – –

Fn = Fn (I1, I2,…In ; tn = Fn setelah ?tn

F ( kapital ) = Sinyal steady state dengan asumsi tidak ada delay.

t ( kecil ) = Sifat dinamis dari sinyal yang dapat berubah selama interval waktu ?t.

PROSEDUR PERANCANGAN

a. Pokok permasalahan sudah ditentukan yaitu jumlah input yang dibutuhkan serta jumlah output yang tertentu.

b. Susun kedalam tabel kebenaran (Truth Table).

c. Kondisi don’t care dapat diikut sertakan apabila tidak mempengaruhi output.

DECODER

Decoder adalah rangkaian kombinasi yang akan memilih salah satu keluaran sesuai dengan konfigurasi input. Decoder memiliki n input dan 2^n output.

Blok Diagram Decoder.

decoder 2to4

Tabel Kebenaran

RANGKAIAN LOGIKA

Untuk merancang rangkaian kombinasional dapat digunakan Decoder dan eksternal OR gate (rangkaian kombinasi n – input dan m– output dapat diimplementasikan dengan n to 2^n line decoder dan m – OR gate).

Contoh.

Implementasikan suatu Full Adder dengan memakai Decoder dan 2 gerbang OR

Jawab :

Sum = A + B + Cin = ? 1,2,4,7

Carry out = (A + B) Cin + AB = ? 3,5,6,7

Gambar Rangkaian Logika 3 t0 8

ENCODER

Encoder adalah rangkaian kombinasi yang merupakan kebalikan dari Decoder yaitu manghasilkan output kode biner yang berkorespondensi dengan nilai input. Encoder memiliki 2^n input dan n output.

Tabel kebenaran Encoder 4 to 2

MULTIPLEXER ( MUX )

Blok Diagram Logika Mux

PROSEDUR PERANCANGAN RANGKAIAN KOMBINASIONAL DENGAN MUX

1. Buat tabel kebenaran sesuai dengan kondisi input dan output serta nomor Mintermnya.

2. Salah satu variabel input digunakan sebagai Data dan sisanya dari variabel input sebagai address/selector.

3. Buat tabel Implementasi dan lingkari nomor Mintermnya yang sesuai dengan outputnya.

4. Jika 2 Mintermnya dalam satu kolom dilingkari, maka input Mux adalah 1 dan sebaliknya input Mux adalah berlogika 0

5. Jika nomor Mintermnya hanya dilingkari pada salah satu baris dalam kolom yang sama, maka input Mux akan berlogika sesuai dengan baris persamaan pada variabel yang diberikan.

Contoh !

Implementasikan F(ABC) = ?1,3,5,6 dengan Mux (4x 1).

Jawab:

Tabel Kebenaran

Catatan.

Input Variabel A diambil sebagai data sedangkan B dan C sebagai address.

Tabel Implementasi

DEMULTIPLEXER (DEMUX)

Blok Diagram Logika DEMUX

3.

Perbedaan Rangkaian Sekuensial dan Kombinasional

Dari penjelasan diatas kita dapat menyimpulkan bahwa:

·

Rangkaian

kombinasional terdiri dari gerbang logika yang memiliki output yang selalu

tergantung pada kombinasi input yang ada.Rangkaian kombinasional melakukan

operasi yang dapat ditentukan secara logika dengan memakai sebuah fungsi

boolean.

·

Rangkaian

sekuensial merupakan rangkaian logika yang keadaan outputnya tergantung pada

keadaan input-inputnya juga tergantung pada keadaan output sebelumnya.

Rangkaian ini juga didefenisikan sebagai rangkaian logika yang outputnya

tergantung waktu.